最新プロジェクト

Beyond 5G Project

ハードウェア班

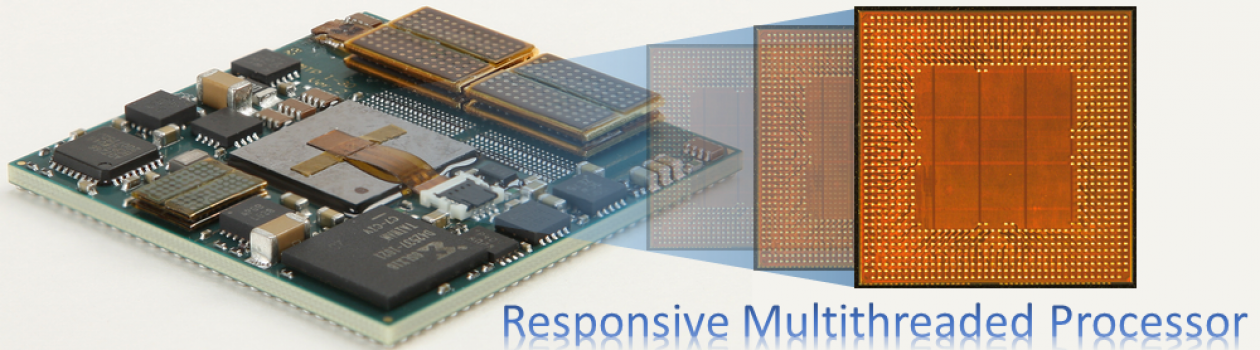

Space Responsive Multithreaded Processor (SRMTP)

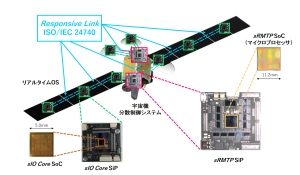

本プロジェクトは、宇宙機制御用分散リアルタイムシステムに関する研究開発を行っています。 ここでリアルタイムとは処理や通信に時間制約(デッドラインや周期等)があることを意味し、分散リアルタイムシステムではその処理や通信が時間制約を守ることで初めて動作を行うことができます。例えば、あるシステムにおけるモータ制御の処理が時間制約を満たさなければ、そのシステムは正常に動作することができず事故の原因となりえます。さらには宇宙環境で動作する宇宙機システムでは宇宙放射線、振動、熱等による影響下でも動作し続けることが要求されます。 我々は宇宙機の分散制御を実現するために、リアルタイム処理用CPU、リアルタイム通信、メモリ、制御用I/O等を1チップのLSIに集積したSoC (System-on-Chip)、当該SoC、DRAM、Flash、コネクタ等を集積した超小型基板であるSiP (System-in-Package)、及びリアルタイムOS (favor) の研究開発を行っています。 具体的には、高機能な分散リアルタイム制御を実現するsRMTP (Space Responsive Multithreaded Processor)には、リアルタイム処理用プロセッサRMT PU (Responsive Multithreaded Processing Unit) 、リアルタイム通信Responsive Link (ISO/IEC 24740) 、エラー訂正機能付きのSRAMやDRAM IF、各種I/O (UART, PWM, GPIO等)を1チップのSoCに集積しています。RMT PUは、優先度付き同時マルチスレッド実行、各プログラムの速度を制御するIPC制御機構 、コンテキストスイッチのオーバヘッドを削減するコンテキストキャッシュ、割り込みによるスレッド起床機構等を有し、細粒度のリアルタイム処理を行うことができます。Responsive Linkは任意のトポロジーでノード間通信を行うことができ、パケットに付与された優先度に従って各ノードでパケットの追い越しが可能なのでプリエンプティブなリアルタイム通信を行うことができます。 また、sIO CoreはシンプルなCPU、Responsive Link、及び各種制御用I/Oを1チップに集積したSoCであり、比較的単純な分散制御ノードを容易に構築することを可能にします。 これらのsRMTP及びsIO Coreはシステムレベル、アーキテクチャレベル、及びプロセスレベルのディペンダビリティを有すように設計しており、マルチレベルディペンダビリティを実現します。 我々のこれらの技術は宇宙機に限らず、あらゆる分散リアルタイムシステムに応用可能です。

Dependable Responsive Multithreaded Processor I (D-RMTP I)

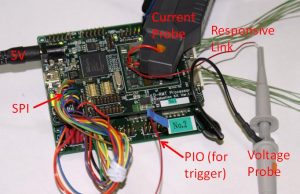

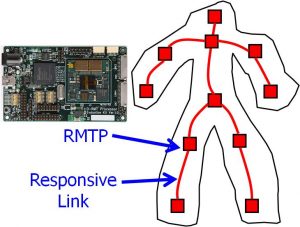

山﨑研究室では、主に組込みリアルタイムシステム(特に分散制御システム)に関する研究開発を行っています。組込みリアルタイムシステムとは、例えば自動車、ファクトリーオートメーション、宇宙船、およびヒューマノイドロボットなどに代表される、時間制約を有した特定の制御機能のために設計されたコンピュータシステムのことです。これらのシステムは、リアルタイム処理アーキテクチャ、リアルタイム通信、およびリアルタイムOSといった重要な技術の上に構築されます。さらに、近年はディペンダビリティの必要性が高まっており、すでに社会インフラの一部として使用されている組込みリアルタイムシステムにおいてますます重要になってきています。山﨑研究室では、上記のアーキテクチャや通信規格、OS、およびアプリケーションを独自に設計・実装・評価を行っています。また、それらのバックグラウンドとなる理論の考案も行っています。評価に関して、ディペンダビリティを「信頼性、可用性、安全性、保守性」を併せ持つ性質と定義し、各性質について様々な評価指標を設けています。 我々は、特にヒューマノイドロボット向けに独自プロセッサDependable Responsive Multithreaded Processor I(D-RMTP I)を設計しました。D-RMTP Iはリアルタイムプロセッシングユニット(RMT PU)やノード間リアルタイム通信用のResponsive Link、他にもIEEE1394、PCI-X、イーサネット、PWM、SPIなどを含む様々なI/O周辺機器を統合したSystem-on-Chip(SoC)の形になっています。さらに、D-RMTP I SoCやDDR-SDRAM、フラッシュメモリ、電源回路、各種センサが積層され、30mm角D-RMTP I System-in-Package(SiP)中に実装されています。D-RMTP I SiPは運動制御用にヒューマノイドロボットの関節内に埋め込まれる制御プロセッサとして使用されます。30mm角のように小さなサイズであることは、ヒューマノイドロボットのような実際の組込みシステムでは強く要求されます。

Responsive Link

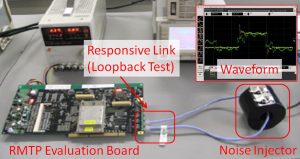

Responsive Linkは、分散リアルタイムシステム(例:ヒューマノイドロボット)のためのノード間通信規格(ISO/IEC 24740:2008)です。Responsive Linkでは、物理的に分離された2種類のリンクを定義しています。ハードリアルタイム制約を持った、サイズが小さく低レイテンシの通信向けのイベントリンクと、ソフトリアルタイム制約を持った、高スループットの通信向けのデータリンクです。リアルタイム通信では、優先度の高いパケットが優先的に処理されることが重要となります(リアルタイムスケジューリングにおけるタスクのプリエンプションと同様)。そこで、複数のパケットが同じ出力ポートを要求するとき、高優先度パケットが常に優先的に出力されるように、パケットの優先度に基づいてクロスバースイッチが割り当てられます。また、同じノード宛で異なる優先度を持つ複数のパケットに対して、異なるルーティングパスが割り当てられるように、ルーティングは宛先と優先度をペアとしてルーティングテーブルエントリを定義します。さらに、通信の信頼性を向上させるために、様々なエラー検出訂正(ECC)コードとラインコードが実装されています。通信環境とノイズパラメータは動的に変更されるので(例:自動車、ロボット)、ECCコードとラインコードの最適な組み合わせは、優先度及びノイズパラメータに応じて動的に選択されます。

リアルタイムマルチプロセッサ向けIPC制御機構

アプリケーションのリアルタイム実行は、我々のインフラのために使用される多くの組込みリアルタイムシステムにとって重要な要件の一つです。このようなリアルタイムスケジューリングはタスクの最悪実行時間(WCET)に依存していますが、WCET解析は近年のシステム(例:SMT, OoO, DVFS)の複雑さのためにますます悲観的になっています。このような悲観的なWCET解析では、アプリケーションのパフォーマンスが低下してしまいます。そこで、我々はWCET解析に依存しないで、クロックあたりの命令数(IPC: Instructions Per Clock cycle)を直接制御するアプローチを提案しています。つまり、各タスクに対して目標IPCを指定することができ、IPC制御機構を備えたマイクロプロセッサは目標IPCを満たすように命令をコミットします。IPC制御にはフィードフォワード制御あるいはPID制御が使われ、動的に目標値との誤差を修正して精度を向上させます。IPC制御機構はD-RMTP I上に実装され、その実用性はD-RMTP I評価ボードで検証されています。

リアルタイムネットワークオンチップ

製造技術の進歩によりチップマルチプロセッサ(CMP)の数は増加し、バスのような従来の相互接続構造では大規模のCMPに対して十分な拡張性を提供することはできません。近年は、Network-on-Chip(NoC)が大規模のCMP向けのスケーラブルな相互接続として広く使用されています。優先度に基づくパケットを転送するNoCはQoSをサポートし、CMP上の時間制約を保証するする必要があります。負荷が低いと低優先度パケットは正確に処理されますが、負荷が高くなると優先度逆転が発生します。この場合、高優先度パケットの通信遅延が低優先度パケットによって増加してしまいます。そこで、優先度逆転を低減すべく、優先度継承やVirtual Channel Stealing(VCS)方式が提案され、ハードウェアコストやネットワーク性能の観点から評価されています。評価結果より、VCS方式は最高優先度パケットの通信遅延を改善し、優先度の逆転を低減することを示しています。

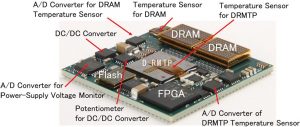

Dependable Responsive Multithreaded Processor II (D-RMTP II)

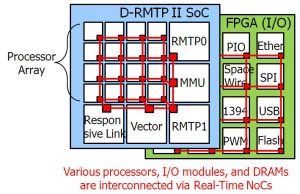

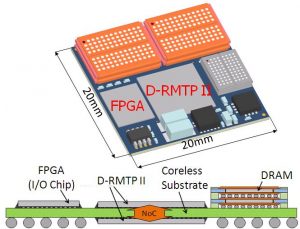

プロセッサ、メモリモジュール、および様々なサイズ、機能、速度を持つI/Oデバイスで構成されるヘテロジニアスマルチコアアーキテクチャは、ヒューマノイドロボットのような高性能組込みシステムのための有望な解決策の一つです。D-RMTP IIは、このようなヘテロジニアスマルチコア機能をサポートする、D-RMTP Iの後継です。D-RMTP II SiPはD -RMTP II SoC、DRAMチップ、および専用I/Oコントローラチップで構成されています。 D-RMTP II SoCは2個のRMT Processor(RMTP0, RMTP1)、並列プロセッサアレイ(8個のMIPSライクなプロセッサ)、ベクトルプロセッサ、およびResponsive Linkコントローラを統合しています。I/Oチップは、例えば、IEEE1394、PCI-X、イーサネット、PWM、SPIのような様々なI/Oコントローラを有します。D-RMTP II SoCは65nmプロセス技術を用いて、ASICとして実装されており、I/OチップはFPGA上に実装されています。それらすべてはリアルタイムチップ間ネットワークで相互接続されています。SoCとSiPの開発と並行して、我々は、効率良いメモリ管理のための分散Translation-Lookaside Buffer(TLB)などのヘテロジニアスマルチコアアーキテクチャにおいて重要な技術を調査しています。

参考文献

- Kazutoshi Suito, Rikuhei Ueda, Kei Fujii, Takuma Kogo, Hiroki Matsutani and Nobuyuki Yamasaki, “The Dependable Responsive Multithreaded Processor for Distributed Real-Time Systems,” IEEE Micro, Vol. 32, No. 6, pp. 52-61, December, 2012.

- Nobuyuki Yamasaki, “Responsive Link for Distributed Real-Time Processing,” Proc. of the 10th International Workshop on Innovative Architecture for Future Generation High-Performance Processors and Systems (IWIA’07), pp.20-29, Jan 2007.

- Kohei Matsumoto, Hiroyuki Umeo, and Nobuyuki Yamasaki, “A Thread Speed Control Scheme for Real-time Microprocessors,” Proc. of the 1st International Workshop on Cyber-Physical Systems, Networks, and Applications (CPSNA’11), pp.21-16, Aug 2011.

- Masakazu Taniguchi, Hiroki Matsutani, and Nobuyuki Yamasaki, “Design and Implementation of On-chip Adaptive Router with Predictor for Regional Congestion,” Proc. of the 1st International Workshop on Cyber-Physical Systems, Networks, and Applications (CPSNA’11), pp.22-27, Aug 2011.

- Nobuyuki Yamasaki, “Co-Design of Dependable Responsive Multithreaded Processor II (DRMTP-II) SoC and SiP,” The International Workshop on Innovative Architecture for Future Generation High-Performance Processors and Systems (IWIA) 2014, March 2014.

- Kawase Daiki, Kazutoshi Suito, Hiroki Matsutani, and Nobuyuki Yamasaki, “Design and Implementation of Distributed TLB Mechanism for Heterogeneous Multi-Core Processors,” IEICE Technical Reports CPSY2011-84 (ETNET’12), Vol.111, No.461, pp.85-90, Mar 2012.

ソフト班

リアルタイムスケジューリング理論

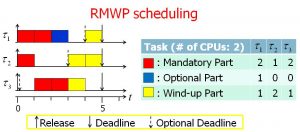

ヒューマノイドロボットのような分散リアルタイムシステムは、動的な環境における過負荷問題に直面しています。タスクの時間制約を満たしつつ結果の精度を高めるために、インプリサイス計算モデルが提案されています。インプリサイス計算モデルでは、タスクは必須部分(mandatory parts)と付加部分(optional parts)に分けられます。必須部分はリアルタイム性が要求されるクリティカルな処理部分であり、付加部分は必須部分が生成した結果の精度を高める非リアルタイムの処理部分です。システムが過負荷状態に陥って付加部分に割り当てる実行時間が無くなったとしても、付加部分を中断することでデッドラインミスを回避することが可能です。インプリサイス計算モデルを用いた固定優先度スケジューリングアルゴリズムとして、我々はRate-Monotonic with Wind-up Part(RMWP)を提案しました。RMWPはシングルプロセッサとマルチプロセッサの両方に対して適用可能です。スケジュール可能性解析により、RMWPではタスクのデッドライン、周期、最悪実行時間およびCPU利用率といった与えられたパラメータが条件を満たしたときに、どのタスクもデッドラインまでに実行を完了できることが理論的に証明されています。

リアルタイムスケジューリング解析

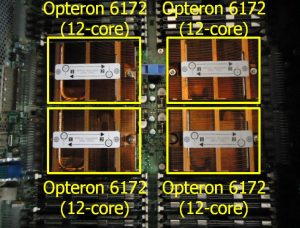

我々はシミュレーションや実機を用いた実験を通してリアルタイムスケジューリングアルゴリズムを広く評価してきました。シミュレーション評価では、タスクのスケジュール成功率に基づいてアルゴリズムの理論的なスケジュール可能性を評価します。実機評価では、リアルタイムOSを用いて実際に生じるスケジューリングオーバヘッドを測定します。オーバヘッドはスケジュール成功率に著しく影響し、ハードウェアアーキテクチャ(例:IBM x3755 48 CPUs, D-RMTP I)、レディキュー(例:O(1)スケジューラ、二項ヒープキュー、双方向循環リスト)、リアルタイムスケジューリングアルゴリズム(例:EDF, RM, RMWP)、スケジューリングポリシ(グローバル、パーティション、セミパーティション、クラスタ)に依存します。

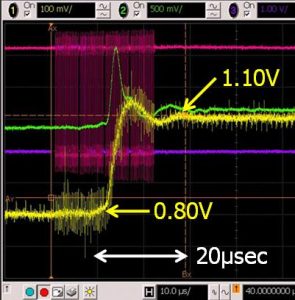

リアルタイム動的電圧周波数制御

近年、携帯電話やヒューマノイドロボットなどの組込みリアルタイムシステムには、時間制約だけでなく、低消費電力や高性能も要求されます。動的に供給電圧と動作周波数を制御するDynamic Voltage and Frequency Scaling(DVFS)は、エネルギー効率を向上させるために様々なシステムに使用されています。しかしながら、システム実行時に電圧と周波数が変更された場合、オーバヘッドとエネルギーの損失が発生します。特に、電圧遷移に要する時間は厳しい時間制約を持つ組込みリアルタイムシステムにとっては深刻な問題となります。我々はリアルタイムスケジューリング解析に電圧遷移の遅延を考慮することで時間制約を保証できるリアルタイムDVFS (RT-DVFS) を提案しています。実際の電圧遷移の遅延やエネルギーの損失はRT-DVFSのための重要なパラメータであるので、我々はD-RMTP I評価ボード上の電圧遷移の遅延やエネルギーの損失を実機で測定しました。そして、測定した電圧遷移の遅延を考慮したRT-DVFSを提案し、高いスケジューリング成功率とエネルギー削減率を達成することを示しました。

RMT Processor向けリアルタイムOS

ITRON仕様に基づくリアルタイムOSは、広く日本の産業で使用されてきました。我々はRMT Processor固有の機能を使用してパフォーマンスと予測可能性を向上させるために、ITRONベースのOSを拡張しました。例えば、RMT Processorに固有のスレッド制御命令はコンテキスト切り替えオーバヘッドを低減するためのスレッドの作成とディスパッチに使用されます。同時に実行されるスレッドの数が増加する場合、最悪割り込み応答時間を維持するために専用スレッドが割込み処理に割り当てられます。RMT Processorの評価ボードを用いた実験結果では、マルチスレッド拡張はカーネルのコードサイズと実行時間を増加させたものの、コンテキストスイッチを含むサービスコールはハードウェアによるコンテキストスイッチによって高速化されたことを示しました。また、スレッド制御命令を使用することによる高速なコンテキストスイッチでタスクのスケジュール可能性が向上しました。

リアルタイム通信スケジューリング

リアルタイム通信ネットワークは、時間的制約を有するソフトウェアまたはハードウェアを統合した分散システムにとって必要不可欠です。例えば、現代のヒューマノイドロボットには、運動制御のために数十もの制御プロセッサが関節内に埋め込まれています。従って、これらの制御プロセッサ間で優先度に基づくアービトレーションを用いて与えられた通信デッドラインを保証することができるリアルタイム通信が、正確な運動制御に必須であると考えられます。Responsive Linkを備えたD-RMTP Iは、そのような目的のために設計されています。 通信のデッドラインとその優先度は、運動制御の通信要件に応じて、各送信元および宛先ノードのペアに対して決定されます。我々は与えられたデッドラインに違反することなく、通信スケジュール可能性を最大限に高めることができるリアルタイム通信スケジューリングアルゴリズムを研究しています。

参考文献

- Hiroyuki Chishiro and Nobuyuki Yamasaki, “Global Semi-fixed-priority Scheduling on Multiprocessors,” Proc. of the 17th IEEE International Conference on Embedded and Real-Time Computing Systems and Applications (RTCSA’11), pp.218-223, Aug 2011.

- Hiroyuki Chishiro and Nobuyuki Yamasaki, “Experimental Evaluation of Global and Partitioned Semi-Fixed-Priority Scheduling Algorithms on Multicore Systems,” Proc. of the 15th IEEE International Symposium on Object/Component/Service-Oriented Real-Time Distributed Computing (ISORC’12), pp.127-134, Apr 2012.

- Kei Fujii, Hiroyuki Chishiro, Hiroki Matsutani, and Nobuyuki Yamasaki, “Dynamic Voltage and Frequency Scaling for Real-Time Scheduling on a Prioritized SMT Processor,” Proc. of the 1st International Workshop on Cyber-Physical Systems, Networks, and Applications (CPSNA’11), pp.9-15, Aug 2011.

- Rikuhei Ueda, Kei Fujii, Hiroyuki Chishiro, Hiroki Matsutani, and Nobuyuki Yamasaki, “An Extension of Real-Time OS for Multithreaded Processors,” Proc. of the 18th IEEE Real-Time and Embedded Technology and Applications Symposium (RTAS’12), Work-In-Progress session, Apr 2012. (to appear)

- Osamu Yoshizumi, Hiroki Matsutani, and Nobuyuki Yamasaki, “Packet Routing for Distributed Real-Time System on Real-Time Communication Link,” Proc. of the 28th ISCA International Conference on Computers and Their Applications (CATA’13), pp. 197-204, March, 2013.

- Yusuke Kumura, Kazutoshi Suito, Hiroki Matsutani and Nobuyuki Yamasaki, “A Low-Power Link Speed Control Method on Distributed Real-Time Systems,” 2013 IEEE 7th International Symposium on Embedded Multicore Socs, pp. 49-54, September, 2013.