The page for lectures in the autumn term was set up.

Please attend the first class to get an account name and a password necessary for browsing.

ETNET 2017

Matsui presented at CPSY/IPSJ-EMB/IPSJ-SLDM/DC in Kume Island, Japan.

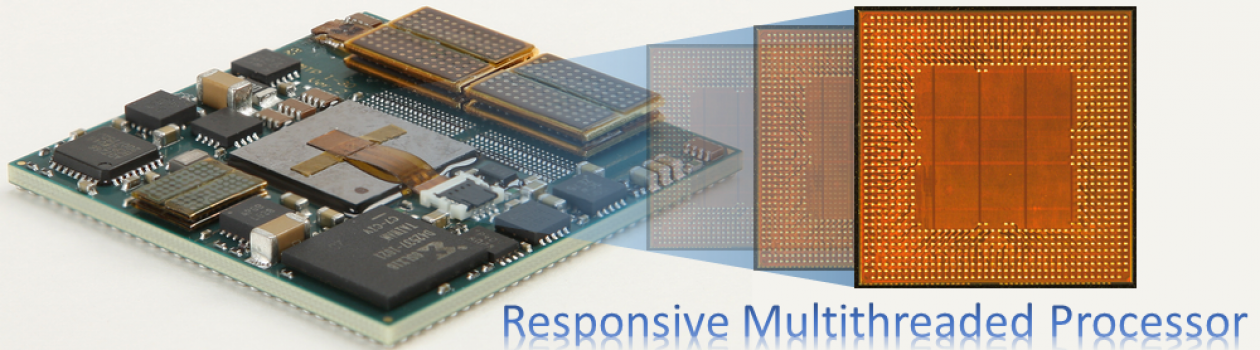

Tsukasa Matsui and Nobuyuki Yamasaki, “An Improvement of Vector Units on RMT Processor for Real-Time Processing ” IEICE Technical Report, Mar 2017.

Pages for lectures in spring term

The page for lectures in the spring term was set up.

Please attend the first class to get an account name and a password necessary for browsing.

Pages for B3

The page for B3 is here.

Only available in Japanese.

Pages for lectures in autumn term

The page for lectures in the autumn term was set up.

Please attend the first class to get an account name and a password necessary for browsing.

Pages for lectures in spring term

The page for lectures in the spring term was set up.

Please attend the first class to get an account name and a password necessary for browsing.

About additional lab. briefing

Information for b3 updated. here

KEIO TECHNO-MALL 2015

We will be exhibited at KEIO TECHNO-MALL 2015, which will be held in Tokyo International Forum on December 4th (Fri.), 2015.

ET/IoT2015

We will be exhibited at Embedded Technology/IoT Technology 2015, which will be held in PACIFICO YOKOHAMA on November 18th (Wed.) to 20th (Fri.), 2015.

Page for B3

The page for B3 is here.

Only available in Japanese.